# K9K2G08X0A

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

#### ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

- 1. For updates or additional information about Samsung products, contact your nearest Samsung office.

- 2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

<sup>\*</sup> Samsung Electronics reserves the right to change products or specification without notice.

### **Document Title**

# 256M x 8 Bit NAND Flash Memory

### **Revision History**

| Revision No | History                                                                                                                                                                                       | Draft Date    | Remark      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

| 0.0         | 1. Initial issue                                                                                                                                                                              | May. 31. 2004 | Advance     |

| 0.1         | <ol> <li>Technical note is changed</li> <li>Notes of AC timing characteristics are added</li> <li>The description of Copy-back program is changed</li> <li>TSOP package is deleted</li> </ol> | Oct. 25. 2004 | Preliminary |

| 0.2         | 1. CE access time: 23ns->35ns (p.9)                                                                                                                                                           | Feb. 14. 2005 |             |

| 0.3         | <ol> <li>The value of tREA is changed. (18ns-&gt;20ns)</li> <li>EDO mode is added.</li> </ol>                                                                                                 | May 4 2005    |             |

| 0.4         | 1. The flow chart to creat the initial invalid block table is changed.                                                                                                                        | May 6 2005    |             |

| 1.0         | <ol> <li>1. 1.8V FBGA spec is merged</li> <li>2. 3.3V FBGA package is added</li> <li>3. FBGA package size is changed to 9.5 x 12</li> <li>4. Leaded part is deleted</li> </ol>                | Feb. 1 2006   |             |

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.

### 256M x 8 Bit NAND Flash Memory

#### **PRODUCT LIST**

| Part Number  | Vcc Range    | Organization | PKG Type |

|--------------|--------------|--------------|----------|

| K9K2G08U0A-F | 2.7 ~ 3.6V   | X8           | WSOP1    |

| K9K2G08X0A-J | 1.65 ~ 1.95V | X8           | FBGA     |

#### **FEATURES**

- Voltage Supply

- 2.7 V ~3.6 V

- 1.65V ~ 1.95V

- Organization

- Memory Cell Array

- (256M + 8,192K)bit x 8bit

- Data Register

- (2K + 64)bit x8bit

- Automatic Program and Erase

- Page Program

- (2K + 64)Byte

- Block Erase

- (128K + 4K)Byte

- Page Read Operation

- Page Size

- 2K-Byte

- Random Read : 25μs(Max.) - Serial Access : 50ns(Min.)

- Fast Write Cycle Time

- Program time : 300μs(Typ.)

- Block Erase Time: 2ms(Typ.)

- Command/Address/Data Multiplexed I/O Port

- Hardware Data Protection

- Program/Erase Lockout During Power Transitions

- Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention: 10 Years

- Command Register Operation

- Unique ID for Copyright Protection

- Package :

- K9K2G08U0A-FIB0

- 48 Pin WSOP I (12x17x0.7mm)- Pb-free Package

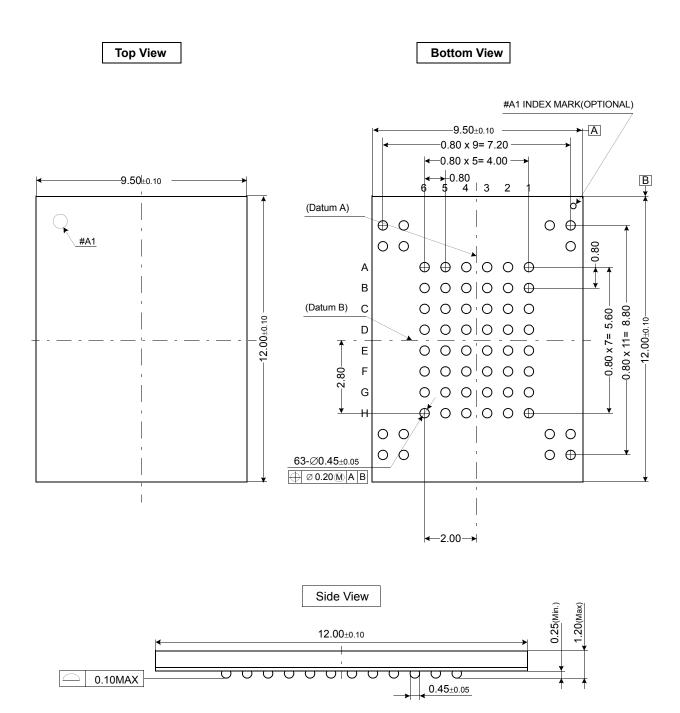

- K9K2G08X0A-JCB0/JIB0

- 63- Ball FBGA (9.5x12) Pb-free Package

#### **GENERAL DESCRIPTION**

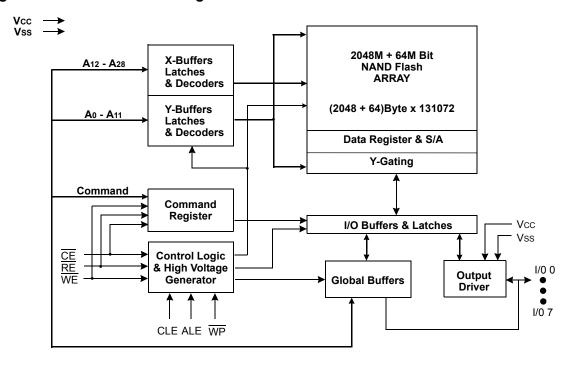

Offered in 256Mx8bit the K9K2G08X0A is 2G bit with spare 64M bit capacity. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation can be performed in typical 300µs on the 2112byte page and an erase operation can be performed in typical 2ms on a 128K-byte block. Data in the data page can be read out at 50ns cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the K9K2G08X0A's extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm. The K9K2G08X0A is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.

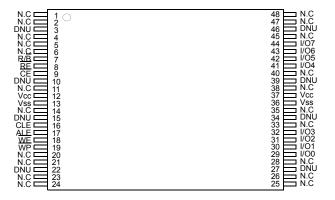

### **PIN CONFIGURATION (WSOP1)**

#### K9K2G08U0A-FIB0

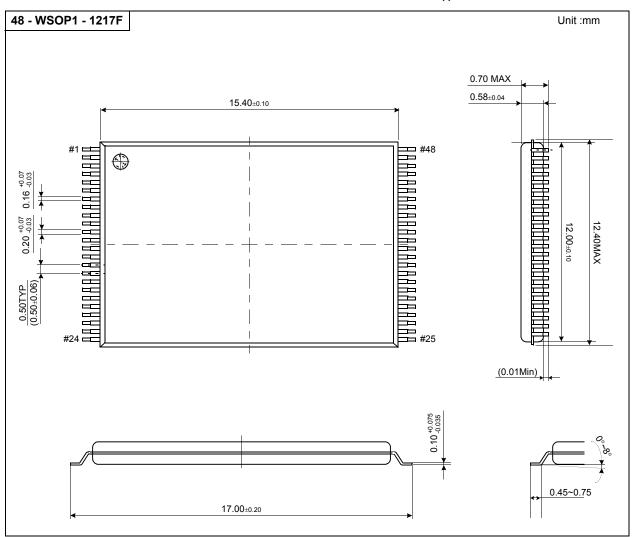

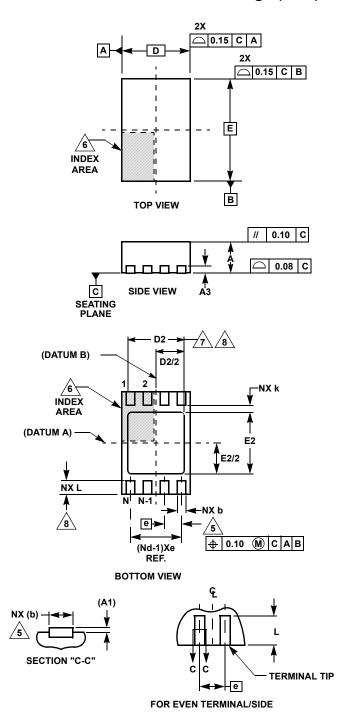

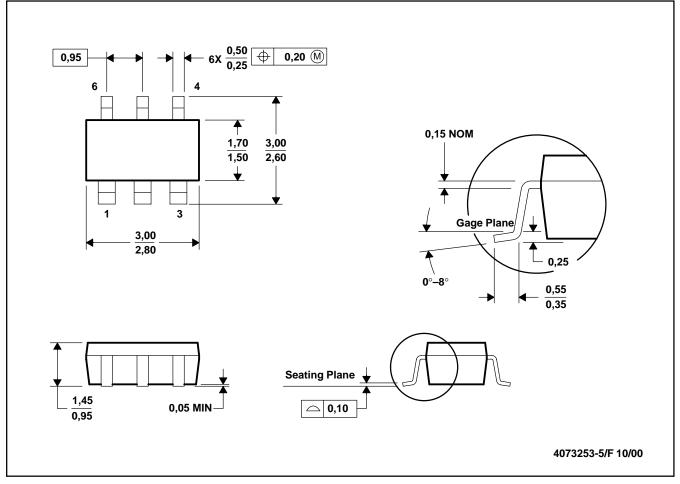

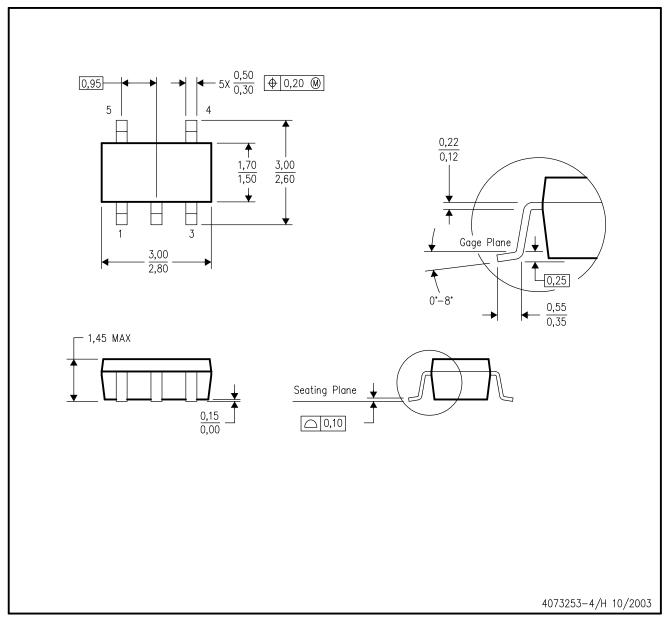

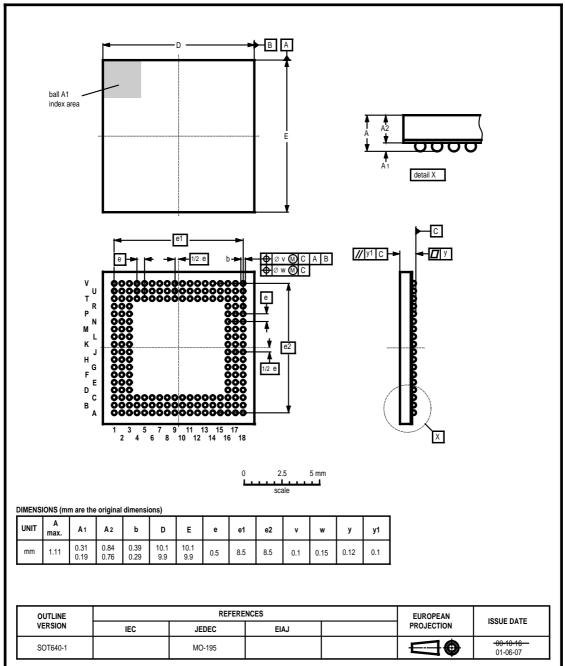

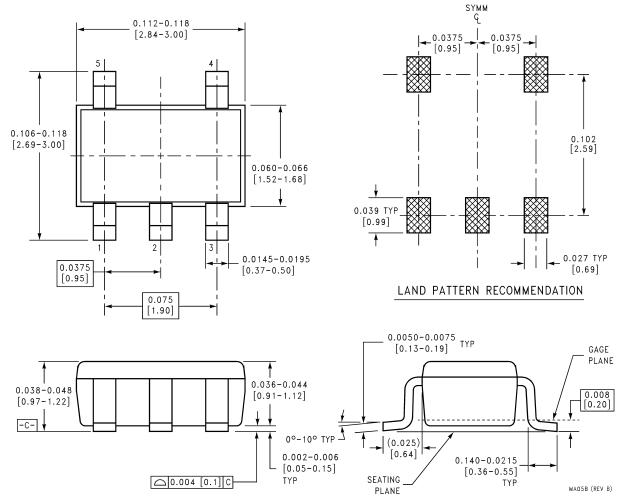

#### **PACKAGE DIMENSIONS**

48-PIN LEAD PLASTIC VERY VERY THIN SMALL OUT-LINE PACKAGE TYPE (I)

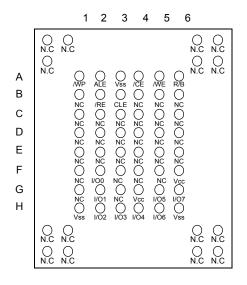

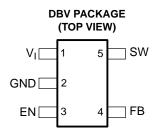

### **PIN CONFIGURATION (FBGA)**

#### K9F1G08X0A-JCB0/JIB0

Top View

### PACKAGE DEMENSIONS(FBGA)

#### **PIN DESCRIPTION**

| Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/00 ~ 1/07 | DATA INPUTS/OUTPUTS  The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.                                                                                                                      |

| CLE         | COMMAND LATCH ENABLE  The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the WE signal.                                                                                                   |

| ALE         | ADDRESS LATCH ENABLE  The ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WE with ALE high.                                                                                                                                                             |

| CE          | CHIP ENABLE The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and the device does not return to standby mode in program or erase opertion. Regarding CE control during read operation, refer to 'Page read' section of Device operation.                                            |

| RE          | READ ENABLE  The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.                                                                                                             |

| WE          | WRITE ENABLE The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.                                                                                                                                                                                                     |

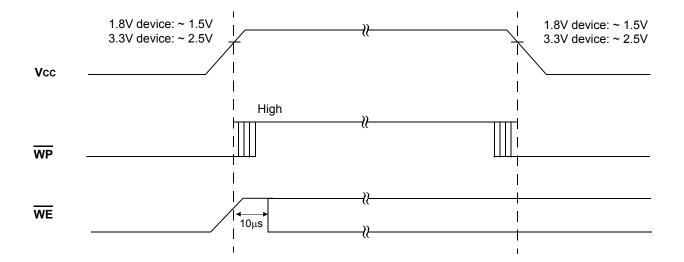

| WP          | WRITE PROTECT The WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the WP pin is active low.                                                                                                                                                                |

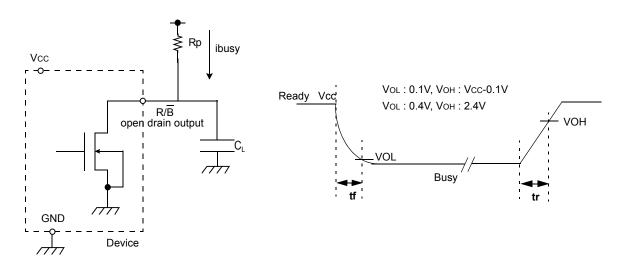

| R/B         | READY/BUSY OUTPUT The R/B output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled. |

| Vcc         | POWER VCC is the power supply for device.                                                                                                                                                                                                                                                                                                 |

| Vss         | GROUND                                                                                                                                                                                                                                                                                                                                    |

| N.C         | NO CONNECTION Lead is not internally connected.                                                                                                                                                                                                                                                                                           |

NOTE:

1. Connect all VCC and VSS pins of each device to common power supply outputs.

2. Do not leave VCC or VSS disconnected.

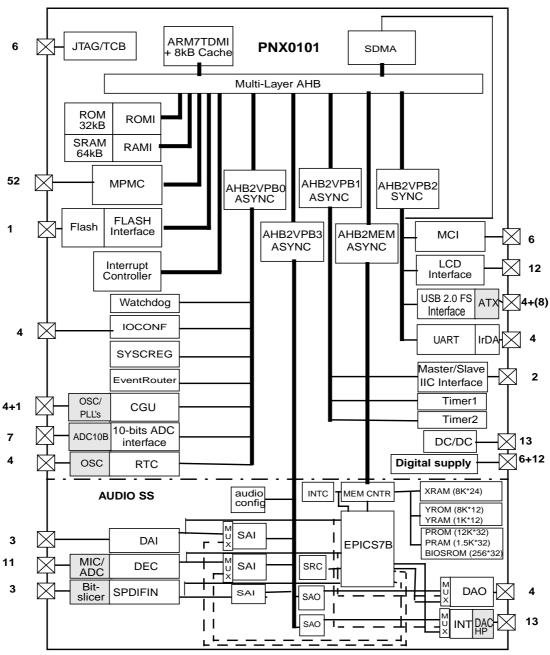

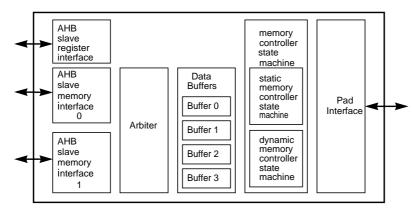

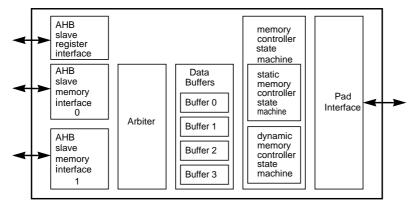

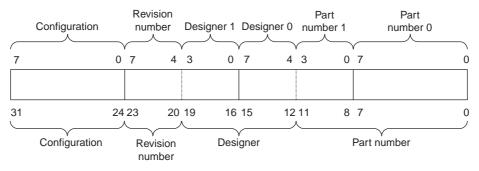

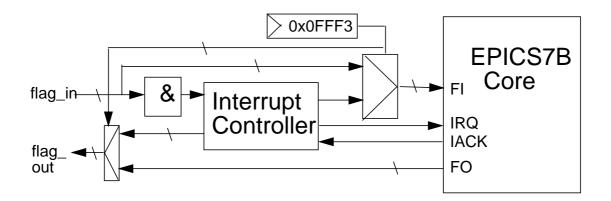

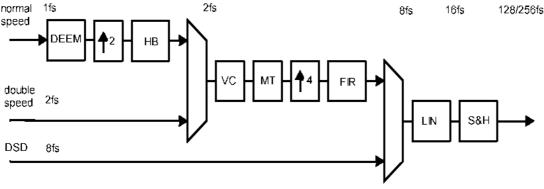

Figure 1. Functional Block Diagram

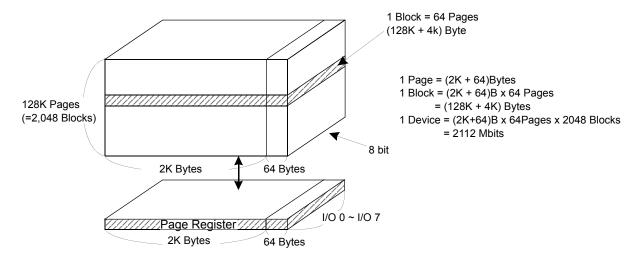

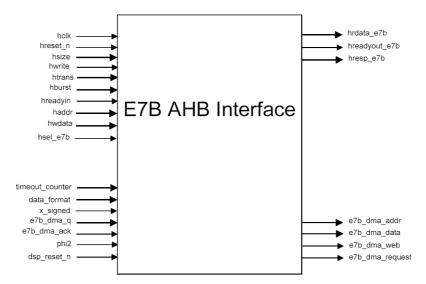

Figure 2 Array Organization

|           | I/O 0       | I/O 1       | I/O 2       | I/O 3       | I/O 4       | I/O 5      | I/O 6          | I/O 7       |

|-----------|-------------|-------------|-------------|-------------|-------------|------------|----------------|-------------|

| 1st Cycle | Ao          | <b>A</b> 1  | <b>A</b> 2  | Аз          | A4          | <b>A</b> 5 | A <sub>6</sub> | A7          |

| 2nd Cycle | <b>A</b> 8  | <b>A</b> 9  | <b>A</b> 10 | A11         | *L          | *L         | *L             | *L          |

| 3rd Cycle | <b>A</b> 12 | <b>A</b> 13 | A14         | <b>A</b> 15 | <b>A</b> 16 | A17        | <b>A</b> 18    | <b>A</b> 19 |

| 4th Cycle | <b>A</b> 20 | <b>A</b> 21 | A22         | A23         | A24         | A25        | <b>A</b> 26    | <b>A</b> 27 |

| 5th Cycle | A28         | *L          | *L          | *L          | *L          | *L         | *L             | *L          |

Column Address Column Address Row Address Row Address Row Address

NOTE: Column Address: Starting Address of the Register.

<sup>\*</sup> The device ignores any additional input of address cycles than required.

<sup>\*</sup> L must be set to "Low".

#### **Product Introduction**

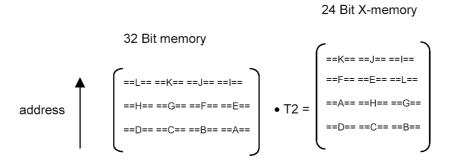

The K9K2G08X0A is a 2112Mbit(2,214,592,512 bit) memory organized as 131,072 rows(pages) by 2112x8 columns. Spare 64 columns are located from column address of 2048~2111. A 2112-byte data register is connected to memory cell arrays for accommodating data transfer between the I/O buffers and memory cells during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block consists of two NAND structures. A NAND structure consists of 32 cells. Total 135,168 NAND cells reside in a block. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 2048 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9K2G08X0A.

The K9K2G08X0A has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Those are latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command and etc require just one cycle bus. Some other commands, like Page Read, Block Erase and Page Program, require two cycles: one cycle for setup and the other cycle for execution. The 264M byte physical space requires 29 addresses, thereby requiring five cycles for addressing: 2 cycles of column address, 3 cycles of row address, in that order. Page Read and Page Program need the same five address cycles following the required command input. In Block Erase operation, however, only the three row address cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9K2G08X0A.

**Table 1. Command Sets**

| Function                        | 1st. Cycle | 2nd. Cycle | Acceptable Command during Busy |

|---------------------------------|------------|------------|--------------------------------|

| Read                            | 00h        | 30h        |                                |

| Read for Copy Back              | 00h        | 35h        |                                |

| Read ID                         | 90h        | -          |                                |

| Reset                           | FFh        | -          | 0                              |

| Page Program                    | 80h        | 10h        |                                |

| Cache Program                   | 80h        | 15h        |                                |

| Copy-Back Program               | 85h        | 10h        |                                |

| Block Erase                     | 60h        | D0h        |                                |

| Random Data Input <sup>-1</sup> | 85h        | -          |                                |

| Random Data Output*1            | 05h        | E0h        |                                |

| Read Status                     | 70h        |            | 0                              |

NOTE: 1. Random Data Input/Output can be executed in a page.

2. Cache program and Copy-Back program are supported only with 3.3V device.

Caution: Any undefined command inputs are prohibited except for above command set of Table 1.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          |                  | Symbol   | Rat                        | Unit          |       |

|------------------------------------|------------------|----------|----------------------------|---------------|-------|

|                                    |                  | Syllibol | 1.8V DEVICE 3.3V DEVICE    |               | Oilit |

| Voltage on any pin relative to Vss |                  | VIN/OUT  | -0.6 to + 2.45             | -0.6 to + 4.6 | V     |

|                                    |                  | Vcc      | -0.6 to + 2.45             | -0.6 to + 4.6 | V     |

| Temperature Under                  | K9K2G08X0A-XCB0  | TBIAS    | -10 to +125<br>-40 to +125 |               | - °C  |

| Bias                               | K9K2G08X0A-XIB0  | IBIAS    |                            |               |       |

| K9K2G08X0A-XCB0                    |                  | Тото     | 05 to 1450                 |               | °C    |

| Storage Temperature                | K9K2G08X0A-XJIB0 | Тѕтс     | -65 to +150                |               | -0    |

| Short Circuit Current              |                  | los      | 5                          |               | mA    |

- Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.

Maximum DC voltage on input/output pins is Vcc,+0.3V which, during transitions, may overshoot to Vcc+2.0V for periods <20ns.

- 2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### RECOMMENDED OPERATING CONDITIONS

(Voltage reference to GND, :Ta=0 to 70°C, K9K2G08X0A-XIB0:Ta=-40 to 85°C)

| Parameter      | Symbol | K9K2G08R0A(1.8V) |      |      | K9l | Unit |     |       |

|----------------|--------|------------------|------|------|-----|------|-----|-------|

| Parameter      | Symbol | Min              | Тур. | Max  | Min | Тур. | Max | Offic |

| Supply Voltage | Vcc    | 1.65             | 1.8  | 1.95 | 2.7 | 3.3  | 3.6 | V     |

| Supply Voltage | Vss    | 0                | 0    | 0    | 0   | 0    | 0   | V     |

### DC AND OPERATING CHARACTERISTICS (Recommended operating conditions otherwise noted.)

| Parameter                                                                  |                                 | Symbol                        | Test Conditions                                                     | K9K2    | G08R0 | A(1.8V) | K9K20   | 08U0 | A(3.3V) | Unit |

|----------------------------------------------------------------------------|---------------------------------|-------------------------------|---------------------------------------------------------------------|---------|-------|---------|---------|------|---------|------|

| r                                                                          | rarameter                       | ameter Symbol rest conditions |                                                                     | Min     | Тур   | Max     | Min     | Тур  | Max     | Unit |

| Operat-                                                                    | Page Read with<br>Serial Access | lcc1                          | tRC=50ns, (30ns with 3.3V device)<br>CE=V <sub>IL</sub><br>IOUT=0mA | -       | 10    | 20      | -       | 10   | 30      |      |

| Current                                                                    | Program                         | Icc2                          | -                                                                   | -       | 10    | 20      | -       | 10   | 30      | mA   |

|                                                                            | Erase                           | Icc3                          | -                                                                   | -       | 10    | 20      | -       | 10   | 30      |      |

| Stand-by                                                                   | Current(TTL)                    | Is <sub>B</sub> 1             | CE=VIH, WP=0V/Vcc                                                   | -       | -     | 1       | -       | -    | 1       |      |

| Stand-by Current(CMOS) IsB2                                                |                                 | IsB2                          | <u>CE</u> =Vcc-0.2,<br><u>WP</u> =0V/Vcc                            | -       | 20    | 100     | -       | 20   | 100     |      |

| Input Leakage Current ILI                                                  |                                 | ILI                           | Vin=0 to Vcc(max)                                                   | -       | -     | ±20     | -       | -    | ±10     | μА   |

| Output L                                                                   | eakage Current                  | ILO                           | Vout=0 to Vcc(max)                                                  | -       | -     | ±20     | -       | -    | ±10     |      |

| Input Hig                                                                  | gh Voltage                      | ViH                           | -                                                                   | 0.8xVcc | -     | Vcc+0.3 | 0.8xVcc | -    | Vcc+0.3 |      |

| Input Low Voltage, All inputs                                              |                                 | VIL                           | -                                                                   | -0.3    | -     | 0.2xVcc | -0.3    | -    | 0.2xVcc |      |

| Output High Voltage VoH                                                    |                                 | Vон                           | K9K2G08R0A: IoH=-100μA<br>K9K2G08U0A: IoH=-400μA                    | Vcc-0.1 | -     | -       | 2.4     | -    | -       | ٧    |

| Output Low Voltage Level VoL K9K2G08R0A: IoL=100mA K9K2G08U0A: IoL=2.1mA   |                                 | -                             | -                                                                   | 0.1     | -     | -       | 0.4     |      |         |      |

| Output Low Current(R/B) IOL(R/B) K9K2G08R0A: VoL=0.1V K9K2G08U0A: VoL=0.4V |                                 | 3                             | 4                                                                   | -       | 8     | 10      | -       | mA   |         |      |

#### **VALID BLOCK**

| Parameter          | Symbol | Min  | Тур. | Max  | Unit   |

|--------------------|--------|------|------|------|--------|

| Valid Block Number | N∨B    | 2008 | -    | 2048 | Blocks |

#### NOTE:

- 1. The K9K2G08X0A may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or program factory-marked bad blocks. Refer to the attached technical notes for appropriate management of invalid blocks.

- 2. The 1st block, which is placed on 00h block address, is fully guaranteed to be a valid block and does not require Error Correction up to 1K Program/ Earase cycles...

#### **AC TEST CONDITION**

(K9K2G08X0A-XCB0:TA=0 to 70°C, K9K2G08X0A-XIB0:TA=-40 to 85°C

K9K2G08R0A: Vcc=1.65V~1.95V, K9K2G08U0A: Vcc=2.7V~3.6Vunless otherwise noted)

| Parameter                      | K9K2G08R0A             | K9K2G08U0A             |

|--------------------------------|------------------------|------------------------|

| Input Pulse Levels             | 0V to Vcc              | 0V to Vcc              |

| Input Rise and Fall Times      | 5ns                    | 5ns                    |

| Input and Output Timing Levels | Vcc/2                  | Vcc/2                  |

| Output Load                    | 1 TTL GATE and CL=30pF | 1 TTL GATE and CL=50pF |

#### CAPACITANCE(TA=25C, VCC=1.8V/3.3V, f=1.0MHz)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input/Output Capacitance | Ci/O   | VIL=0V         | -   | 20  | pF   |

| Input Capacitance        | Cin    | VIN=0V         | -   | 20  | pF   |

NOTE: Capacitance is periodically sampled and not 100% tested.

#### MODE SELECTION

| CLE | ALE              | CE | WE       | RE | WP                    | Mode               |                       |  |  |

|-----|------------------|----|----------|----|-----------------------|--------------------|-----------------------|--|--|

| Н   | L                | L  | <b>□</b> | Н  | Х                     | Read Mode          | Command Input         |  |  |

| L   | Н                | L  |          | Н  | Х                     | rtcau Mouc         | Address Input(5clock) |  |  |

| Н   | L                | L  | F        | Н  | Н                     | Write Mode         | Command Input         |  |  |

| L   | Н                | L  | F        | Н  | Н                     | vviite ivioue      | Address Input(5clock) |  |  |

| L   | L                | L  | F        | Н  | Н                     | Data Input         |                       |  |  |

| L   | L                | L  | Н        | ₹  | Х                     | Data Output        |                       |  |  |

| Х   | Х                | Х  | Х        | Н  | Х                     | During Read        | (Busy)                |  |  |

| Х   | Х                | Х  | Х        | Х  | Н                     | During Progr       | ram(Busy)             |  |  |

| Х   | Х                | Х  | Х        | Х  | Н                     | During Erase(Busy) |                       |  |  |

| Х   | X <sup>(1)</sup> | Х  | Х        | Х  | L                     | Write Protect      |                       |  |  |

| Х   | Х                | Н  | Х        | Х  | 0V/Vcc <sup>(2)</sup> | Stand-by           |                       |  |  |

NOTE: 1. X can be VIL or VIH.

### **Program / Erase Characteristics**

| Parameter                         | Symbol      | Min     | Тур | Max | Unit |        |

|-----------------------------------|-------------|---------|-----|-----|------|--------|

| Program Time                      |             | tPROG*1 | -   | 200 | 700  | μS     |

| Dummy Busy Time for Cache Program |             | tcbsy*2 |     | 3   | 700  | μs     |

| Number of Partial Program Cycles  | Main Array  | Non     | -   | -   | 4    | cycles |

| in the Same Page                  | Spare Array | Nop     | -   | -   | 4    | cycles |

| Block Erase Time                  |             | tBERS   | -   | 2   | 3    | ms     |

NOTE: 1.Typical program time is defined as the time within which more than 50% of whole pages are programmed at Vcc of 3.3V and 25°C

2. Max. time of tcBSY depends on timing between internal program completion and data in

<sup>2.</sup> WP should be biased to CMOS high or CMOS low for standby.

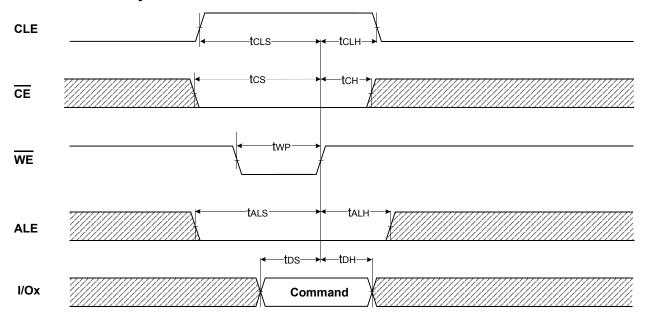

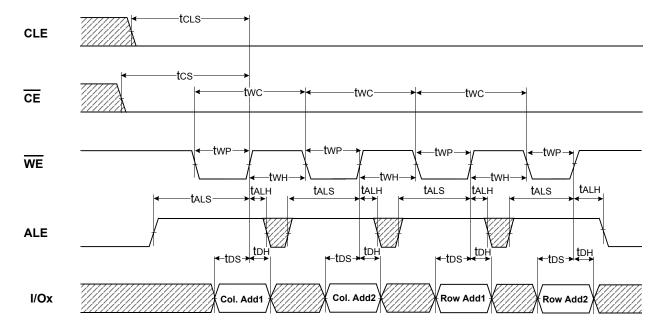

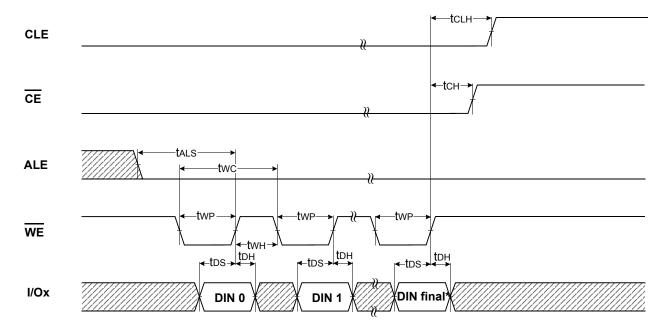

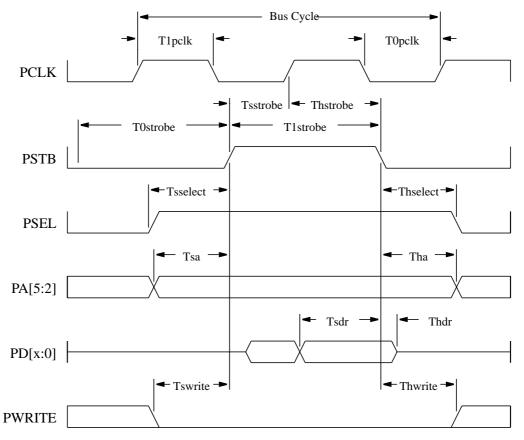

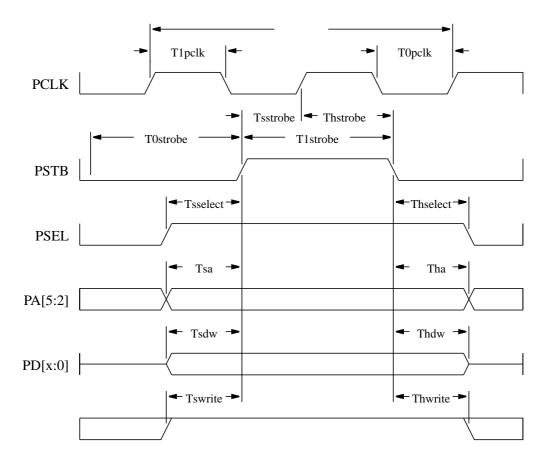

### AC Timing Characteristics for Command / Address / Data Input

|                              | M                  | lin               | M          |            |            |       |

|------------------------------|--------------------|-------------------|------------|------------|------------|-------|

| Parameter                    | Symbol             | IVI               | III        | IVI        | ax         | Unit  |

| T diameter                   | Cymbol             | K9K2G08R0A        | K9K2G08U0A | K9K2G08R0A | K9K2G08U0A | Oilit |

| CLE setup Time               | tcls*1             | 25                | 15         | -          | -          | ns    |

| CLE Hold Time                | tclh               | 10                | 5          | -          | -          | ns    |

| CE setup Time                | tcs*1              | 35                | 20         | -          | -          | ns    |

| CE Hold Time                 | tсн                | 10                | 5          | -          | -          | ns    |

| WE Pulse Width               | twp                | 25                | 15         | -          | -          | ns    |

| ALE setup Time               | tals*1             | 25                | 15         | -          | -          | ns    |

| ALE Hold Time                | talh               | 10                | 5          | -          | -          | ns    |

| Data setup Time              | tDS*1              | 20                | 15         | -          | -          | ns    |

| Data Hold Time               | tон                | 10                | 5          | -          | -          | ns    |

| Write Cycle Time             | twc                | 45                | 30         | -          | -          | ns    |

| WE High Hold Time            | twн                | 15                | 10         | -          | -          | ns    |

| Address to Data Loading Time | tadl <sup>*2</sup> | 100 <sup>*2</sup> | 100*2      | -          | -          | ns    |

NOTE: 1. The transition of the corresponding control pins must occur only once while WE is held low.

2. tADL is the time from the WE rising edge of final address cycle to the WE rising edge of first data cycle.

3. For cache program operation, the whole AC Charcateristics must be same as that of K9K2G08R0A.

### **AC Characteristics for Operation**

| Parameter                                  | Symbol | М          | in         | M                      | Unit       |      |

|--------------------------------------------|--------|------------|------------|------------------------|------------|------|

| Parameter                                  | Symbol | K9K2G08R0A | K9K2G08U0A | K9K2G08R0A             | K9K2G08U0A | Unit |

| Data Transfer from Cell to Register        | tr     | -          | -          | 25                     | 25         | μS   |

| ALE to RE Delay                            | tar    | 10         | 10         | -                      | -          | ns   |

| CLE to RE Delay                            | tclr   | 10         | 10         | -                      | -          | ns   |

| Ready to RE Low                            | trr    | 20         | 20         | -                      | -          | ns   |

| RE Pulse Width                             | trp    | 25         | 15         | -                      | -          | ns   |

| WE High to Busy                            | twB    | -          | -          | 100                    | 100        | ns   |

| Read Cycle Time                            | trc    | 50         | 30         | -                      | -          | ns   |

| RE Access Time                             | trea   | -          | -          | 30                     | 20         | ns   |

| CE Access Time                             | tCEA   | -          | -          | 45                     | 35         | ns   |

| RE High to Output Hi-Z                     | trhz   | -          | -          | 30                     | 30         | ns   |

| CE High to Output Hi-Z                     | tcHZ   | -          | -          | 20                     | 20         | ns   |

| RE or CE High to Output hold               | tон    | 15         | 15         | -                      | -          | ns   |

| RE High Hold Time                          | treh   | 15         | 10         | -                      | -          | ns   |

| Output Hi-Z to RE Low                      | tır    | 0          | 0          | -                      | -          | ns   |

| WE High to RE Low                          | twhr   | 60         | 60         | -                      | -          | ns   |

| Device Resetting Time (Read/Program/Erase) | trst   | -          | -          | 5/10/500 <sup>*1</sup> | 5/10/500*1 | μS   |

NOTE: 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.

2. For cache program operation, the whole AC Charcateristics must be same as that of K9K2G08R0A.

#### NAND Flash Technical Notes

#### Initial Invalid Block(s)

Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by Samsung. The information regarding the initial invalid block(s) is so called as the initial invalid block information. Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s) does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select transistor. The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is fully guaranteed to be a valid block, does not require Error Correction up to 1K Program/Erase cycles.

#### Identifying Initial Invalid Block(s)

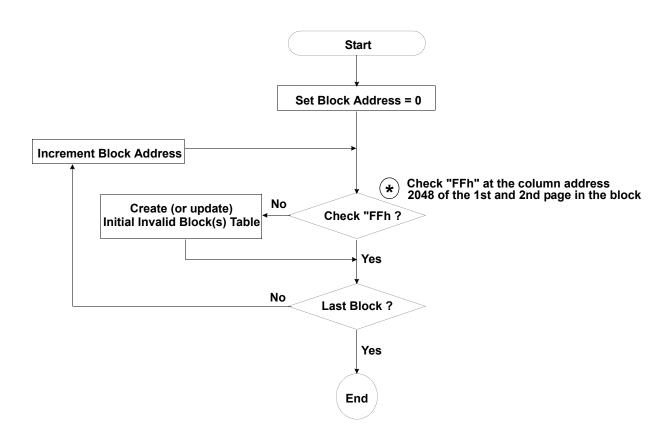

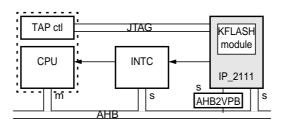

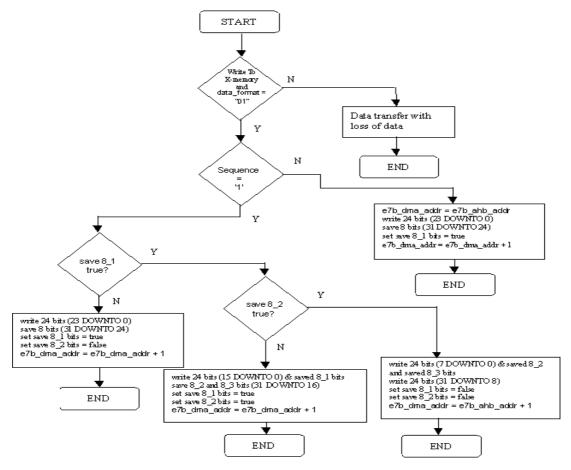

All device locations are erased except locations where the initial invalid block(s) information is written prior to shipping. The initial invalid block(s) status is defined by the 1st byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every initial invalid block has non-FFh data at the column address of 2048. Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the initial invalid block information and create the initial invalid block table via the following suggested flow chart(Figure 3). Any intentional erasure of the initial invalid block information is prohibited.

Figure 3. Flow chart to create initial invalid block table.

### NAND Flash Technical Notes (Continued)

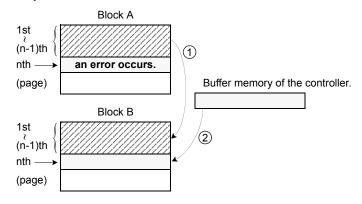

#### Error in write or read operation

Within its life time, additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the block failure rate. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read failure due to single bit error should be reclaimed by ECC without any block replacement. The block failure rate in the qualification report does not include those reclaimed blocks.

| Failure Mode |                    | Detection and Countermeasure sequence        |

|--------------|--------------------|----------------------------------------------|

| Write        | Erase Failure      | Status Read after Erase> Block Replacement   |

| vviile       | Program Failure    | Status Read after Program> Block Replacement |

| Read         | Single Bit Failure | Verify ECC -> ECC Correction                 |

**ECC**

: Error Correcting Code --> Hamming Code etc. Example) 1bit correction & 2bit detection

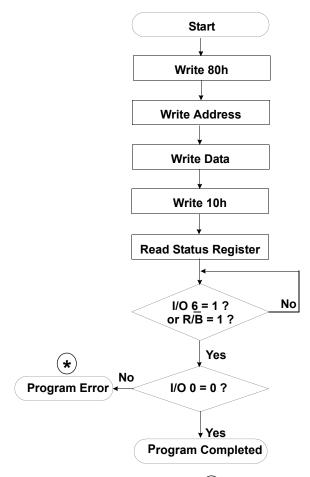

#### **Program Flow Chart**

(\*): If program operation results in an error, map out the block including the page in error and copy the target data to another block.

#### NAND Flash Technical Notes (Continued)

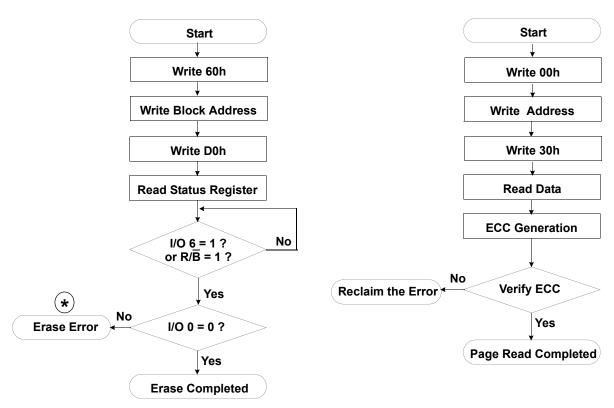

#### **Erase Flow Chart**

### **Read Flow Chart**

\* : If erase operation results in an error, map out the failing block and replace it with another block.

#### **Block Replacement**

<sup>\*</sup> Step1

When an error happens in the nth page of the Block 'A' during erase or program operation.

Copy the data in the 1st ~ (n-1)th page to the same location of another free block. (Block 'B')

Then, copy the nth page data of the Block 'A' in the buffer memory to the nth page of the Block 'B'.

Do not erase or program to Block 'A' by creating an 'invalid Block' table or other appropriate scheme.

<sup>\*</sup> Step2

<sup>\*</sup> Step3

<sup>\*</sup> Step4

### NAND Flash Technical Notes (Continued)

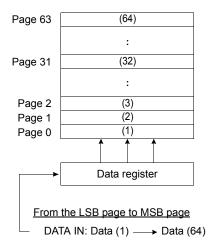

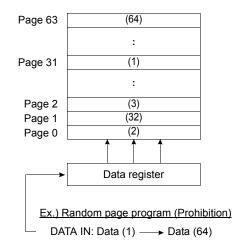

#### Addressing for program operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most significant bit) pages of the block. Random page address programming is prohibited.

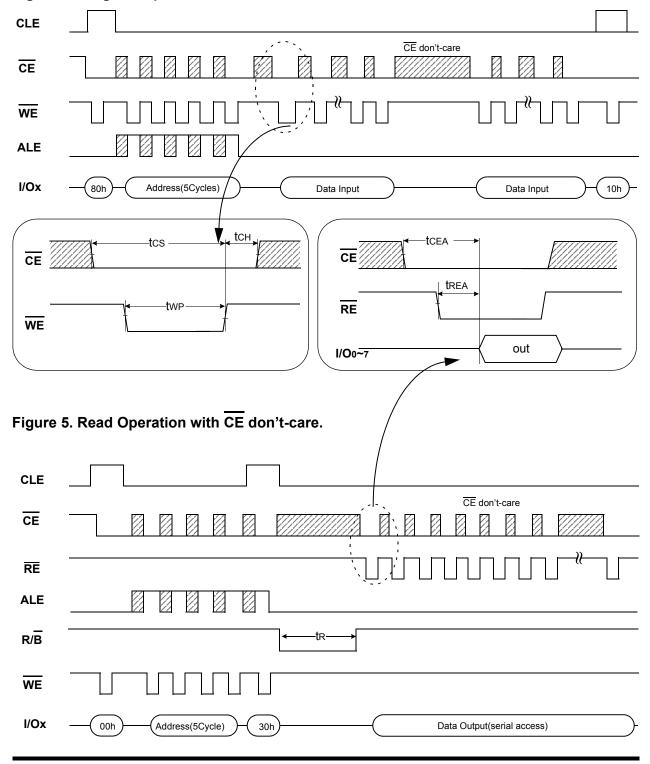

### System Interface Using CE don't-care.

For an easier system interface,  $\overline{\text{CE}}$  may be inactive during the data-loading or serial access as shown below. The internal 2112byte data registers are utilized as separate buffers for this operation and the system design gets more flexible. In addition, for voice or audio applications which use slow cycle time on the order of  $\mu$ -seconds, de-activating  $\overline{\text{CE}}$  during the data-loading and serial access would provide significant savings in power consumption.

Figure 4. Program Operation with CE don't-care.

#### NOTE

| Device     | Dovice I/O DATA |             | ADDRESS   |           |          |          |          |

|------------|-----------------|-------------|-----------|-----------|----------|----------|----------|

| Device     | I/Ox            | Data In/Out | Col. Add1 | Col. Add2 | Row Add1 | Row Add2 | Row Add3 |

| K9K2G08X0A | I/O 0 ~ I/O 7   | ~2112byte   | A0~A7     | A8~A11    | A12~A19  | A20~A27  | A28      |

### **Command Latch Cycle**

### **Address Latch Cycle**

### **Input Data Latch Cycle**

NOTES: DIN final means 2112

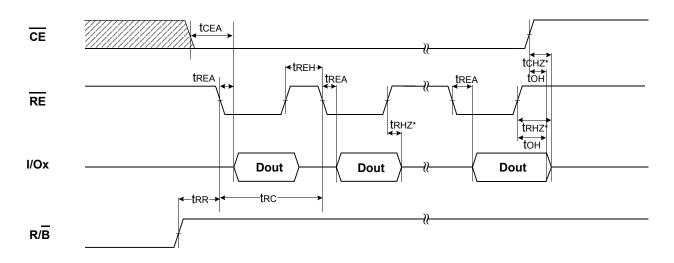

### Serial Access Cycle after Read(CLE=L, $\overline{\text{WE}}$ =H, ALE=L)

NOTES: Transition is measured  $\pm 200$ mV from steady state voltage with load. This parameter is sampled and not 100% tested.

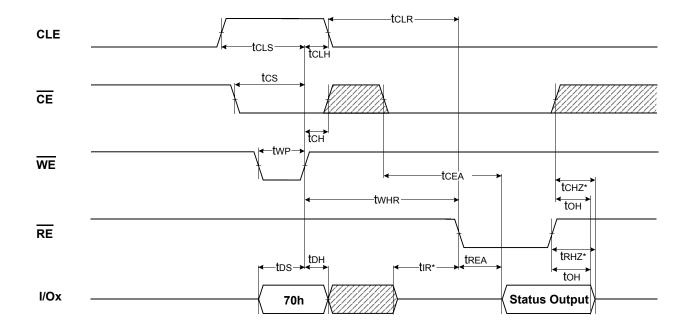

### **Status Read Cycle**

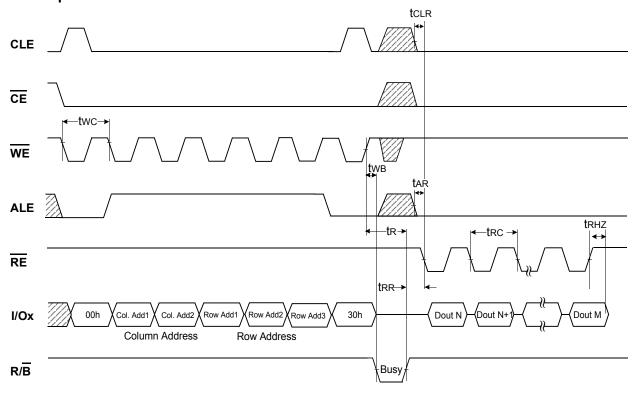

### **Read Operation**

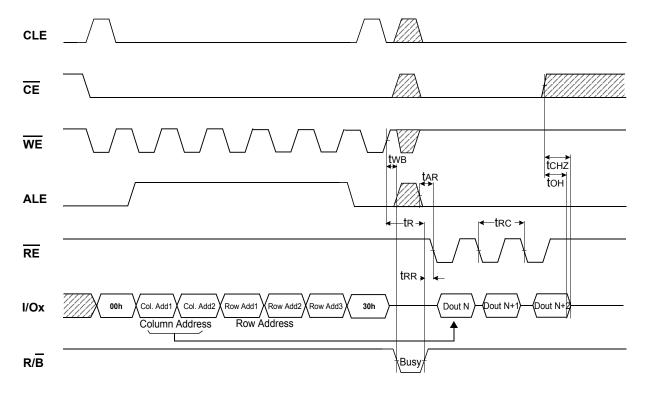

## **Read Operation**(Intercepted by $\overline{\text{CE}}$ )

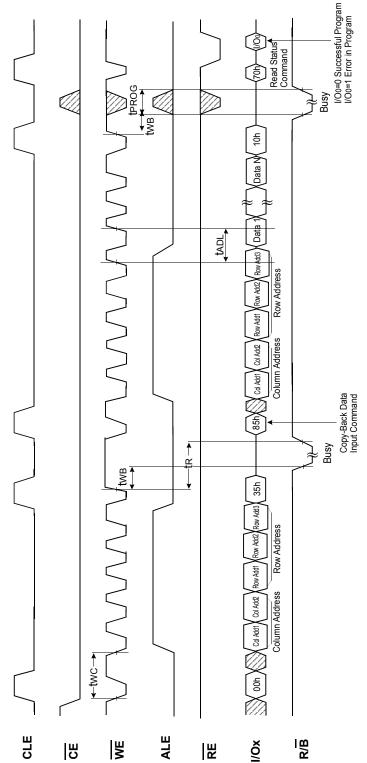

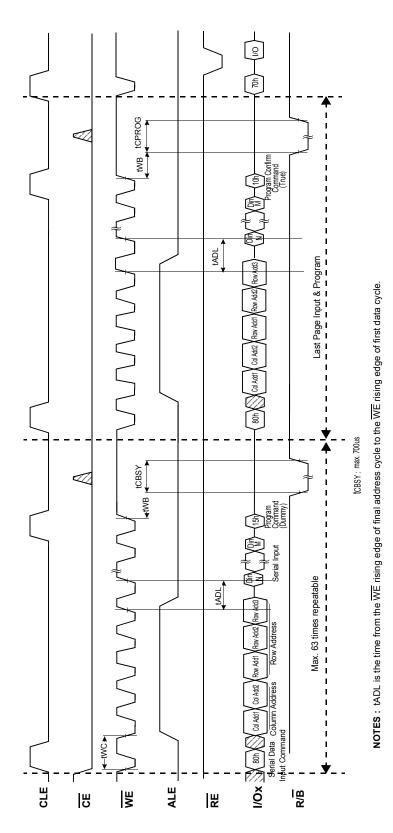

## **Page Program Operation**

**NOTES:** tADL is the time from the  $\overline{\text{WE}}$  rising edge of final address cycle to the  $\overline{\text{WE}}$  rising edge of first data cycle.

**NOTES**: tADL is the time from the  $\overline{\mathrm{WE}}$  rising edge of final address cycle to the  $\overline{\mathrm{WE}}$  rising edge of first data cycle.

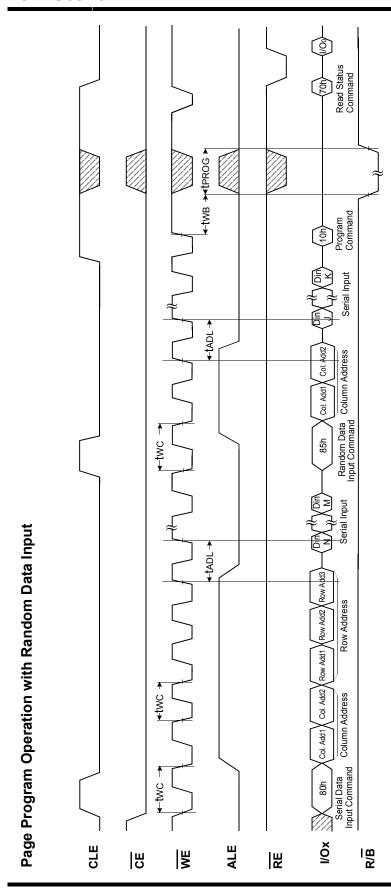

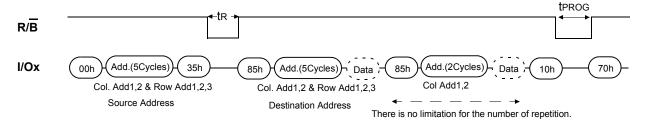

Copy-Back Program Operation With Random Data Input

**NOTES**: tADL is the time from the  $\overline{\mathrm{WE}}$  rising edge of final address cycle to the  $\overline{\mathrm{WE}}$  rising edge of first data cycle.

Cache Program Operation(available only within a block)

Ex.) Cache Program

### **Block Erase Operation**

### **Read ID Operation**

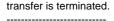

| Device     | Device Code*(2nd Cycle) | 4th Cycle* |

|------------|-------------------------|------------|

| K9K2G08R0A | AAh                     | 15h        |

| K9K2G08U0A | DAh                     | 15h        |

### **ID Defintition Table**

### 90 ID: Access command = 90H

|                      | Description                                     |

|----------------------|-------------------------------------------------|

| 1st Byte             | Maker Code                                      |

| 2 <sup>nd</sup> Byte | Device Code                                     |

| 3 <sup>rd</sup> Byte | Don't care                                      |

| 4 <sup>th</sup> Byte | Page Size, Block Size, Spare Size, Organization |

#### 4th ID Data

|                                        | Description                              | 1/07             | I/O6   | I/O5 I           | /04              | I/O3             | I/O2   | I/O1             | I/O0             |

|----------------------------------------|------------------------------------------|------------------|--------|------------------|------------------|------------------|--------|------------------|------------------|

| Page Size<br>(w/o redundant area )     | 1KB<br>2KB<br>Reserved<br>Reserved       |                  |        |                  |                  |                  |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| Blcok Size<br>(w/o redundant area )    | 64KB<br>128KB<br>256KB<br>Reserved       |                  |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |        |                  |                  |

| Redundant Area Size<br>( byte/512byte) | 8<br>16                                  |                  |        |                  |                  |                  | 0<br>1 |                  |                  |

| Organization                           | x8<br>x16                                |                  | 0<br>1 |                  |                  |                  |        |                  |                  |

| Serial AccessMinimum                   | 50ns<br>Reserved<br>Reserved<br>Reserved | 0<br>1<br>0<br>1 |        |                  |                  | 0<br>0<br>1<br>1 |        |                  |                  |

#### **Device Operation**

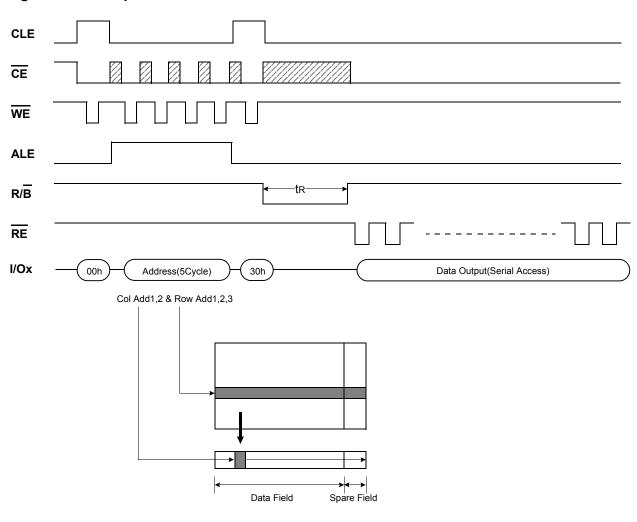

#### **PAGE READ**

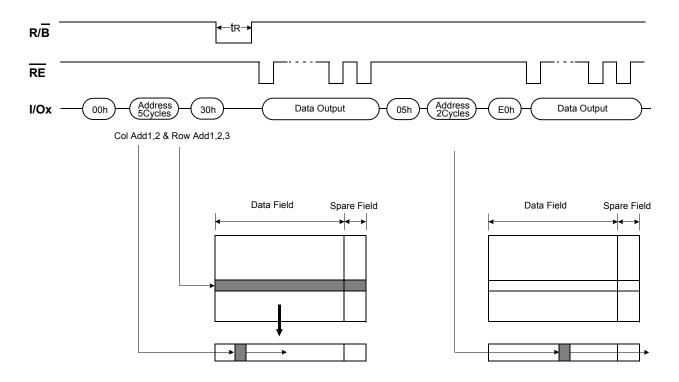

Page read is initiated by writing 00h-30h to the command register along with five address cycles. After initial power up, 00h command is latched. Therefore only five address cycles and 30h command initiates that operation after initial power up. The 2,112 bytes of data within the selected page are transferred to the data registers in less than  $25\mu s(tR)$ . The system controller can detect the completion of this data transfer(tR) by analyzing the output of R/B pin. Once the data in a page is loaded into the data registers, they may be read out in 50ns cycle time by sequentially pulsing RE. The repetitive high to low transitions of the RE clock make the device output the data starting from the selected column address up to the last column address.

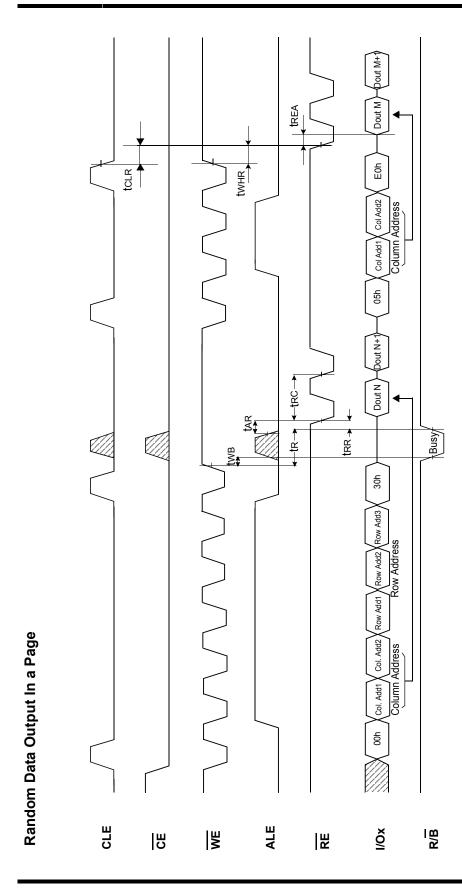

The device may output random data in a page instead of the consecutive sequential data by writing random data output command. The column address of next data, which is going to be out, may be changed to the address which follows random data output command. Random data output can be operated multiple times regardless of how many times it is done in a page.

Figure 6. Read Operation

Figure 7. Random Data Output In a Page

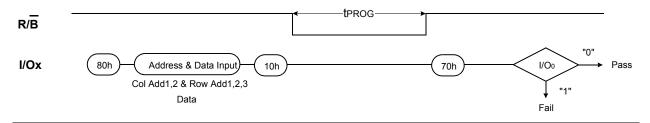

#### PAGE PROGRAM

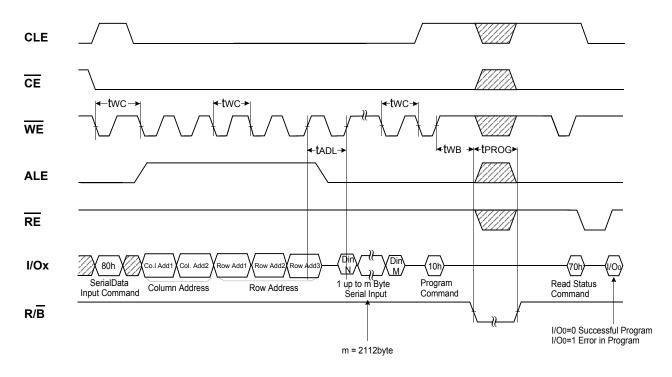

The device is programmed basically on a page basis, but it does allow multiple partial page programing of a word or consecutive bytes up to 2112, in a single page program cycle. The number of consecutive partial page programming operation within the same page without an intervening erase operation must not exceed 4 times for main array(1time/512byte) and 4 times for spare array(1time/16byte). The addressing should be done in sequential order in a block. A page program cycle consists of a serial data loading period in which up to 2112bytes of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

The serial data loading period begins by inputting the Serial Data Input command(80h), followed by the five cycle address inputs and then serial data loading. The words other than those to be programmed do not need to be loaded. The device supports random data input in a page. The column address for the next data, which will be entered, may be changed to the address which follows random data input command(85h). Random data input may be operated multiple times regardless of how many times it is done in a page.

The Page Program confirm command(10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process. The internal write state controller automatically executes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be entered to read the status register. The system controller can detect the completion of a program cycle by monitoring the R/B output, or the Status bit(I/O 6) of the Status Register. Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit(I/O 0) may be checked(Figure 8). The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in Read Status command mode until another valid command is written to the command register.

Figure 8. Program & Read Status Operation

Figure 9. Random Data Input In a Page

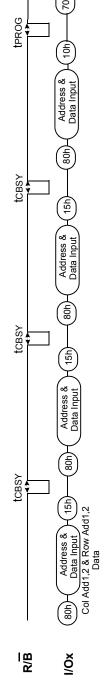

#### **Cache Program**

Cache Program is an extension of Page Program, which is executed with 2112byte data registers, and is available only within a block. Since the device has 1 page of cache memory, serial data input may be executed while data stored in data register are programmed into memory cell.

After writing the first set of data up to 2112byte into the selected cache registers, Cache Program command (15h) instead of actual Page Program (10h) is inputted to make cache registers free and to start internal program operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time(tCBSY) and has its cache registers ready for the next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70h) may be issued to find out when cache registers become ready by polling the Cache-Busy status bit(I/O 6). Pass/fail status of only the previouse page is available upon the return to Ready state. When the next set of data is inputted with the Cache Program command, tCBSY is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit(I/O5) for internal Ready/Busy may be polled to identify the completion of internal programming. If the system monitors the progress of programming only with R/B, the last page of the target programming sequence must be programmed with actual Page Program command (10h). If the Cache Program command (15h) is used instead, status bit (I/O5) must be polled to find out when the last programming is actually finished before starting other operations such as read. Pass/fail status is available in two steps. I/O 1 returns with the status of the previous page upon Ready or I/O6 status bit changing to "1", and later I/O 0 with the status of current page upon true Ready (returning from internal programming) or I/O 5 status bit changing to "1". I/O 1 may be read together when I/O 0 is checked.

Figure 10. Cache Program(available only within a block) tcbsy **t**PROG tcbsy tcbsy R/B Address & Address & Address & Address & 70h 10h 80h 80h 15h Data Input Data Input Data Input\* Data Input Col Add1,2 & Row Add1,2,3 Data Data Data Data tcbsy tcbsy tcbsy R/B I/Ox Address & Address & Status Address & Status 80h 70h 15h) 15h) 15h Data Input Data Input Data Input Col Add1,2 & Row Add1,2,3 Col Add1,2 & Row Add1,2,3 Col Add1,2 & Row Add1,2,3 Data Data Data tcbsy Address & Status 70h Status output 70h 15h Data Input Col Add1,2 & Row Add1,2,3 Data Check I/O1 for pass/fail Check I/O5 for internal ready/busy Check I/O0,1 for pass/fail

**NOTE**: Since programming the last page does not employ caching, the program time has to be that of Page Program. However, if the previous program cycle with the cache data has not finished, the actual program cycle of the last page is initiated only after completion of the previous cycle, which can be expressed as the following formula.

tPROG= Program time for the last page+ Program time for the (last -1)th page

- (Program command cycle time + Last page data loading time)

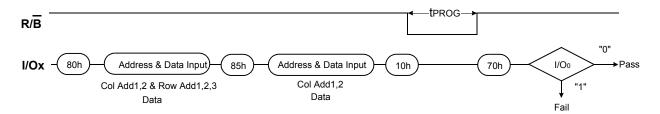

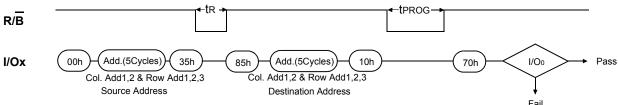

### Copy-Back Program

The copy-back program is configured to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is improved. The benefit is especially obvious when a portion of a block is updated and the rest of the block also need to be copied to the newly assigned free block. The operation for performing a copy-back program is a sequential execution of page-read without serial access and copying-program with the address of destination page. A read operation with "35h" command and the address of the source page moves the whole 2112byte data into the internal data buffer. As soon as the device returns to Ready state, Page-Copy Data-input command (85h) with the address cycles of destination page followed may be written. The Program Confirm command (10h) is required to actually begin the programming operation. Copy-Back Program operation is allowed only within the same memory plane. Once the Copy-Back Program is finished, any additional partial page programming into the copied pages is prohibited before erase. A27 must be the same between source and target page. Data input cycle for modifying a portion or multiple distant portions of the source page is allowed as shown in Figure 11. "When there is a program-failure at Copy-Back operation, error is reported by pass/fail status. But if the source page has an error bit by charge loss, accumulated copy-back operations could also accumulate bit errors. In this case, verifying the source page for a bit error is recommended before Copy-back program"

Figure 11. Page Copy-Back program Operation

NOTE: It's prohibited to operate Copy-Back program from an odd address page(source page) to an even address page(target page) or from an even address page(source page) to an odd address page(target page). Therefore, the Copy-Back program is permitted just between odd address pages or even address pages.

Figure 12. Page Copy-Back program Operation with Random Data Input

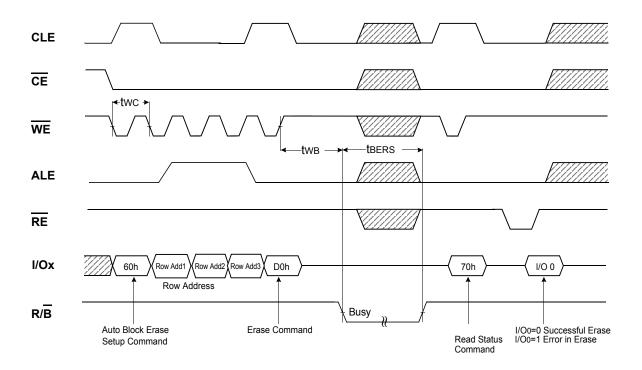

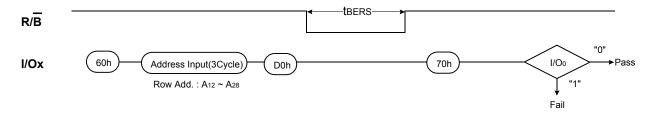

#### **BLOCK ERASE**

The Erase operation is done on a block basis. Block address loading is accomplished in three cycles initiated by an Erase Setup command(60h). Only address A<sub>18</sub> to A<sub>28</sub> is valid while A<sub>12</sub> to A<sub>17</sub> is ignored. The Erase Confirm command(D0h) following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of  $\overline{\text{WE}}$  after the erase confirm command input, the internal write controller handles erase and erase-verify. When the erase operation is completed, the Write Status Bit(I/O 0) may be checked. Figure 13 details the sequence.

Figure 13. Block Erase Operation

#### **READ STATUS**

The device contains a Status Register which may be read to find out whether program or erase operation is completed, and whether the program or erase operation is completed successfully. After writing  $\overline{70}$ h command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of  $\overline{CE}$  or  $\overline{RE}$ , whichever occurs last. This two line control allows the system to poll the progress of each device in multiple memory connections even when  $R/\overline{B}$  pins are common-wired.  $\overline{RE}$  or  $\overline{CE}$  does not need to be toggled for updated status. Refer to table 2 for specific Status Register definitions. The command register remains in Status Read mode until further commands are issued to it. Therefore, if the status register is read during a random read cycle, the read command(00h) should be given before starting read cycles.

**Table2. Read Staus Register Definition**

| I/O No. | Page Program  | Block Erase   | Cache Prorgam   | Read          | Defir           | nition        |

|---------|---------------|---------------|-----------------|---------------|-----------------|---------------|

| I/O 0   | Pass/Fail     | Pass/Fail     | Pass/Fail(N)    | Not use       | Pass : "0"      | Fail : "1"    |

| I/O 1   | Not use       | Not use       | Pass/Fail(N-1)  | Not use       | Pass : "0"      | Fail : "1"    |

| I/O 2   | Not use       | Not use       | Not use         | Not use       | Don't -cared    |               |

| I/O 3   | Not Use       | Not Use       | Not Use         | Not Use       | Don't -cared    |               |

| I/O 4   | Not Use       | Not Use       | Not Use         | Not Use       | Don't -cared    |               |

| I/O 5   | Ready/Busy    | Ready/Busy    | True Ready/Busy | Ready/Busy    | Busy : "0"      | Ready : "1"   |

| I/O 6   | Ready/Busy    | Ready/Busy    | Ready/Busy      | Ready/Busy    | Busy : "0"      | Ready: "1"    |

| I/O 7   | Write Protect | Write Protect | Write Protect   | Write Protect | Protected : "0" | Not Protected |

NOTE: 1. True Ready/Busy represents internal program operation status which is being executed in cache program mode.

2. I/Os defined 'Not use' are recommended to be masked out when Read Status is being executed.

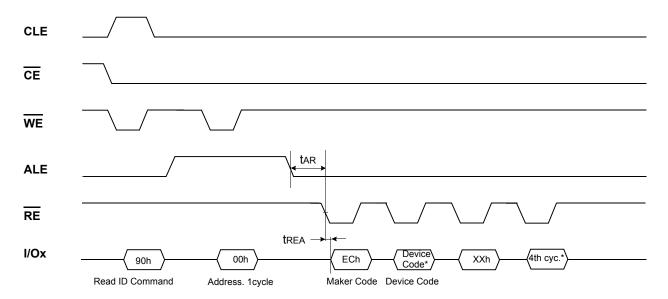

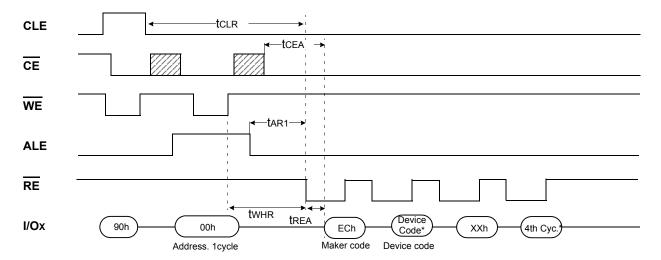

#### Read ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h. Five read cycles sequentially output the manufacturer code(ECh), and the device code and XXh, 4th cycle ID, 15h respectively. The command register remains in Read ID mode until further commands are issued to it. Figure 11 shows the operation sequence.

Figure 14. Read ID Operation

| Device     | Device Code*(2nd Cycle) | 4th Cycle* |

|------------|-------------------------|------------|

| K9K2G08R0A | AAh                     | 15h        |

| K9K2G08U0A | DAh                     | 15h        |

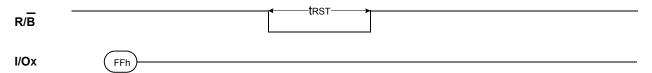

#### RESET

The device offers a reset feature, executed by writing FFh to the command register. When the device is in Busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value C0h when  $\overline{\text{WP}}$  is high. Refer to table 3 for device status after reset operation. If the device is already in reset state a new reset command will be accepted by the command register. The  $R/\overline{B}$  pin transitions to low for tRST after the Reset command is written. Refer to Figure 12 below.

Figure 15. RESET Operation

Table3. Device Status

|                | After Power-up         | After Reset              |

|----------------|------------------------|--------------------------|

| Operation Mode | 00h command is latched | Waiting for next command |

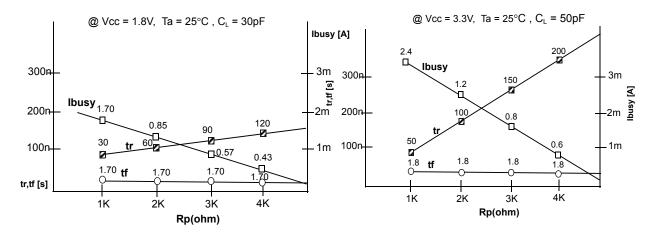

#### **READY/BUSY**

The device has a  $R/\overline{B}$  output that provides a hardware method of indicating the completion of a page program, erase and random read. The  $R/\overline{B}$  pin is normally high but transitions to low after program or erase command is written to the command register or random read is started after address loading. It returns to high when the internal controller has finished the operation. The pin is an opendrain driver thereby allowing two or more  $R/\overline{B}$  outputs to be Or-tied. Because pull-up resistor value is related to  $tr(R/\overline{B})$  and current drain during busy(ibusy) , an appropriate value can be obtained with the following reference chart(Fig 13). Its value can be determined by the following guidance.

Figure 16. Rp vs tr ,tf & Rp vs ibusy

#### Rp value guidance

$$Rp(min, 1.8V part) = \frac{Vcc(Max.) - VoL(Max.)}{IoL + \Sigma IL} = \frac{1.85V}{3mA + \Sigma IL}$$

$$Rp(min, 3.3V part) = \frac{Vcc(Max.) - VoL(Max.)}{IoL + \Sigma IL} = \frac{3.2V}{8mA + \Sigma IL}$$

where IL is the sum of the input currents of all devices tied to the  $R/\overline{B}$  pin.

Rp(max) is determined by maximum permissible limit of tr

## **Data Protection & Power up sequence**

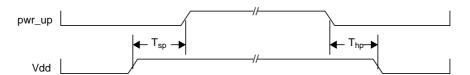

The device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector disables all functions whenever Vcc is below about 1.1V(1.8V device) and 2V(3.3V device).  $\overline{WP}$  pin provides hardware protection and is recommended to be kept at Vil during power-up and power-down. A recovery time of minimum 10µs is required before internal circuit gets ready for any command sequences as shown in Figure 14. The two step command sequence for program/erase provides additional software protection.

Figure 17. AC Waveforms for Power Transition

#### **Extended Data Out Mode**

For the EDO mode, the device should hold the data on the system memory bus until the beginning of the next cycle, so that controller could fetch the data at the falling edge. However NAND flash dosen't support the EDO mode exactly.

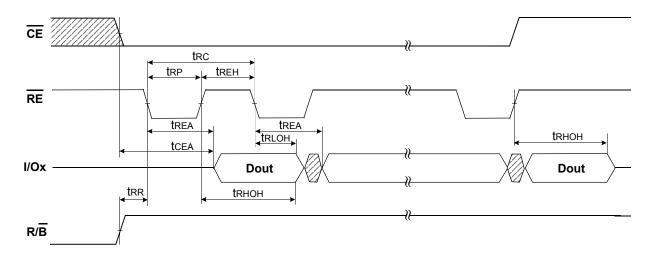

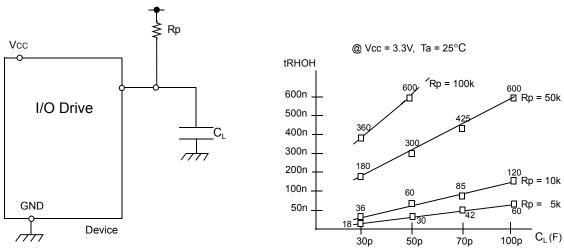

The device stops the data input into the I/O bus after  $\overline{RE}$  rising edge. But since the previous data remains in the I/O bus, the flow of I/O data seems like Figure 18 and the system can access serially the data with EDO mode. tRLOH which is the parameter for fetching data at RE falling time is necessary. Its appropriate value can be obtained with the reference chart as shown in Figure 19. The tRHOH value depands on output load(CL) and I/O bus Pull-up resistor (Rp).

Figure 18. Serial Access Cycle after Read(EDO Type, CLE=L, WE=H, ALE=L)

NOTES: Transition is measured at ±200mV from steady state voltage with load. This parameter is sampled and not 100% tested.

Figure 19. Rp vs tRHOH vs CL

tRLOH / tRHOH value guidance

$tRHOH = C_L * V_{OL} * Rp / Vcc$ tRLOH(min, 3.3V part) = tRHOH - tREH

Data Sheet February 18, 2005 FN9174.0

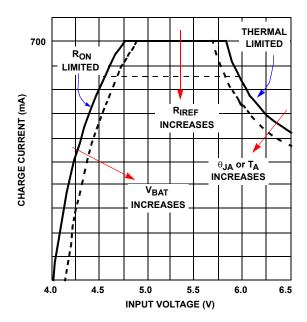

## High Input Voltage Charger

The ISL6294 is a cost-effective, fully integrated high input voltage single-cell Li-ion battery charger. The charger uses a CC/CV charge profile required by Li-ion batteries. The charger accepts an input voltage up to 28V but is disabled when the input voltage exceeds the OVP threshold, typically 6.8V, to prevent excessive power dissipation. The 28V rating eliminates the overvoltage protection circuit required in a low input voltage charger.

The charge current and the end-of-charge (EOC) current are programmable with external resistors. When the battery voltage is lower than typically 2.55V, the charger preconditions the battery with typically 20% of the programmed charge current. When the charge current reduces to the programmable EOC current level during the CV charge phase, an EOC indication is provided by the CHG pin, which is an open-drain output. An internal thermal foldback function protects the charger from any thermal failure.

Two indication pins (PPR and CHG) allow simple interface to a microprocessor or LEDs. When no adapter is attached or when disabled, the charger draws less than  $1\mu A$  leakage current from the battery.

## **Ordering Information**

| PART<br>NUMBER      | TEMP.<br>RANGE (°C) | PACKAGE                   | PKG.<br>DWG. # |

|---------------------|---------------------|---------------------------|----------------|

| ISL6294IRZ (Note)   | -40 to 85           | 8 Ld 2x3 DFN<br>(Pb-free) | L8.2x3         |

| ISL6294IRZ-T (Note) | -40 to 85           | 8 Ld 2x3 DFN<br>(Pb-free) | L8.2x3         |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · Complete Charger for Single-Cell Li-ion/Polymer Batteries

- · Integrated Pass Element and Current Sensor

- · No External Blocking Diode Required

- · Low Component Count and Cost

- 1% Voltage Accuracy

- · Programmable Charge Current

- · Programmable End-of-Charge Current

- Charge Current Thermal Foldback for Thermal Protection

- Trickle Charge for Fully Discharged Batteries

- 28V Maximum Voltage for the Power Input

- · Power Presence and Charge Indications

- Less Than 1µA Leakage Current off the Battery When No Input Power Attached or Charger Disabled

- Ambient Temperature Range: -40°C to 85°C

- 2x3 DFN-8 Packages

- · Pb-Free Available (RoHS Compliant)

## **Applications**

- · Mobile Phones

- · Blue-Tooth Devices

- PDAs

- MP3 Players

- Stand-Alone Chargers

- · Other Handheld Devices

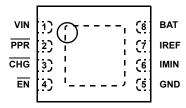

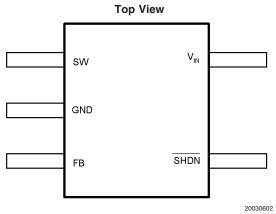

## **Pinout**

**DFN 8 LEAD**TOP VIEW

### Absolute Maximum Ratings (Reference to GND)

| VIN                                            | -0.3V to 30V |

|------------------------------------------------|--------------|

| IMIN, IREF, BAT, CHG, EN, PPR                  | 0.3V to 7V   |

| ESD Rating                                     |              |

| Human Body Model (Per EIA JESD22 Method A114-I | 3) 3kV       |

| Machine Model (Per EIA JED-4701 Method C-111)  | 200V         |

#### **Thermal Information**

| Thermal Resistance                      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| DFN Package (Notes 1, 2)                | 78                     | 11                     |

| Maximum Junction Temperature (Plastic P | ackage)                | 150°C                  |

| Maximum Storage Temperature Range       | 6                      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10  | 0s)                    | 300°C                  |

## **Recommended Operating Conditions**

| Ambient Temperature Range          | 40°C to 85°C   |

|------------------------------------|----------------|

| Maximum Supply Voltage (VIN Pin)   | 28V            |

| Operating Supply Voltage (VIN Pin) | 4.5V to 6.5V   |

| Programmed Charge Current          | 100mA to 700mA |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

#### **Electrical Specifications**

Typical Values Are Tested at VIN = 5V and the Ambient Temperature at 25°C. All Maximum and Minimum Values Are Guaranteed Under the Recommended Operating Supply Voltage Range and Ambient Temperature Range, Unless Otherwise Noted.

| PARAMETER                                | SYMBOL              | TEST CONDITIONS                                      | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------|---------------------|------------------------------------------------------|-------|------|-------|-------|

| POWER-ON RESET                           |                     |                                                      |       |      |       |       |

| Rising POR Threshold                     | V <sub>POR</sub>    | VBAT = 3.0V, use PPR to indicate the                 | 3.3   | 3.9  | 4.3   | V     |

| Falling POR Threshold                    | V <sub>POR</sub>    | comparator output.                                   | 3.1   | 3.6  | 4.15  | V     |

| VIN-BAT OFFSET VOLTAGE                   |                     |                                                      |       |      |       |       |

| Rising Edge                              | Vos                 | V <sub>BAT</sub> = 4.0V, use CHG pin to indicate the | -     | 90   | 150   | mV    |

| Falling Edge                             | Vos                 | comparator output (Note 3)                           | 10    | 50   | -     | mV    |

| OVER VOLTAGE PROTECTION                  |                     |                                                      |       |      |       |       |

| Over Voltage Protection Threshold        | V <sub>OVP</sub>    | (Note 4)                                             | 6.5   | 6.8  | 7.1   | V     |

| OVP Threshold Hysteresis                 |                     | Use PPR to indicate the comparator output            | 100   | 240  | 400   | mV    |

| STANDBY CURRENT                          | 11                  |                                                      |       | l    |       |       |

| BAT Pin Sink Current                     | ISTANDBY            | Charger disabled or the input is floating            | -     | -    | 1.0   | μA    |

| VIN Pin Supply Current                   | I <sub>VIN</sub>    | Charger disabled                                     | -     | 300  | 400   | μA    |

| VIN Pin Supply Current                   | I <sub>VIN</sub>    | Charger enabled                                      | -     | 400  | 600   | μA    |

| VOLTAGE REGULATION                       |                     |                                                      |       |      |       |       |

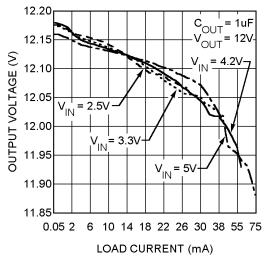

| Output Voltage                           | V <sub>CH</sub>     | 4.3V < V <sub>IN</sub> < 6.5V, charge current = 20mA | 4.158 | 4.20 | 4.242 | V     |

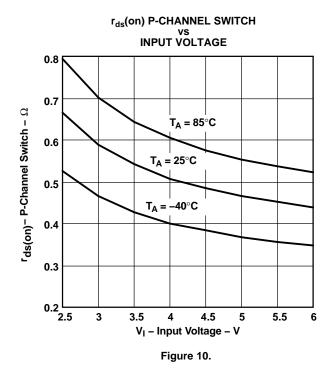

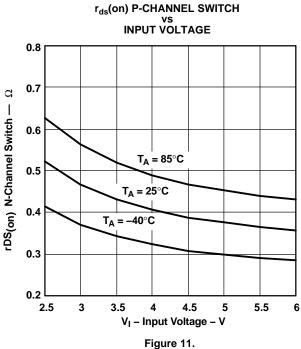

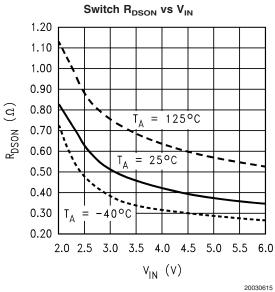

| PMOS On Resistance                       | r <sub>DS(ON)</sub> | V <sub>BAT</sub> = 3.8V, charge current = 0.5A       | -     | 0.6  | -     | Ω     |

| CHARGE CURRENT (Note 5)                  |                     |                                                      |       |      |       |       |

| IREF Pin Output Voltage                  | I <sub>IREF</sub>   | V <sub>BAT</sub> = 3.8V                              | 1.18  | 1.22 | 1.26  | V     |

| Constant Charge Current                  | I <sub>CHG</sub>    | $R_{IREF} = 24.3k\Omega$ , $V_{BAT} = 2.8V - 4.0V$   | 450   | 500  | 550   | mA    |

| Trickle Charge Current                   | I <sub>TRK</sub>    | $R_{IREF}$ = 24.3k $\Omega$ , $V_{BAT}$ = 2.4V       | 70    | 95   | 130   | mA    |

| End-of-Charge Current                    | I <sub>MIN</sub>    | R <sub>IMIN</sub> = 243kΩ                            | 33    | 45   | 57    | mA    |

| EOC Rising Threshold                     |                     | R <sub>IMIN</sub> = 243kΩ                            | 325   | 380  | 415   | mA    |

| PRECONDITIONING CHARGE THRESHO           | LD                  |                                                      | •     |      |       | •     |

| Preconditioning Charge Threshold Voltage | V <sub>MIN</sub>    |                                                      | 2.45  | 2.55 | 2.65  | V     |

| Preconditioning Voltage Hysteresis       | V <sub>MINHYS</sub> |                                                      | 40    | 100  | 150   | mV    |

FN9174.0 intersil February 18, 2005

#### **Electrical Specifications**

Typical Values Are Tested at VIN = 5V and the Ambient Temperature at 25°C. All Maximum and Minimum Values Are Guaranteed Under the Recommended Operating Supply Voltage Range and Ambient Temperature Range, Unless Otherwise Noted. (Continued)

| PARAMETER                                  | SYMBOL                  | TEST CONDITIONS          | MIN | TYP | MAX | UNITS |  |  |

|--------------------------------------------|-------------------------|--------------------------|-----|-----|-----|-------|--|--|

| INTERNAL TEMPERATURE MONITORING            |                         |                          |     |     |     |       |  |  |

| Charge Current Foldback Threshold (Note 6) | T <sub>FOLD</sub>       |                          | 100 | 115 | 130 | °C    |  |  |

| LOGIC INPUT AND OUTPUTS                    | LOGIC INPUT AND OUTPUTS |                          |     |     |     |       |  |  |

| EN Pin Logic Input High                    |                         |                          | 1.3 | -   | -   | V     |  |  |

| EN Pin Logic Input Low                     |                         |                          | -   | -   | 0.5 | V     |  |  |

| EN Pin Internal Pull Down Resistance       |                         |                          | 100 | 200 | 400 | kΩ    |  |  |

| CHG Sink Current when LOW                  |                         | Pin Voltage = 1V         | 10  | 20  | -   | mA    |  |  |

| CHG Leakage Current When HIGH              |                         | V <sub>CHG</sub> = 6.5V  | -   | -   | 1   | μA    |  |  |

| PPR Sink Current when LOW                  |                         | Pin Voltage = 1V         | 10  | 20  | -   | mA    |  |  |

| PPR Leakage Current When HIGH              |                         | V <sub>PPR</sub> 6= 6.5V | -   | -   | 1   | μΑ    |  |  |

#### NOTES:

- 3. The 4.0V V<sub>BAT</sub> is selected so that the CHG output can be used as the indication for the offset comparator output indication. If the V<sub>BAT</sub> is lower than the POR threshold, no output pin can be used for indication.

- 4. For junction temperature below 100 °C.

- 5. The charge current can be affected by the thermal foldback function if the IC under the test setup cannot dissipate the heat.

- 6. This parameter is guaranteed by design, not tested.

## Pin Descriptions

**VIN** - Power input. The absolute maximum input voltage is 28V. A  $0.47\mu F$  or larger value X5R ceramic capacitor is recommended to be placed very close to the input pin for decoupling purpose. Additional capacitance may be required to provide a stable input voltage.

**PPR -** Open-drain power presence indication. The open-drain MOSFET turns on when the input voltage is above the POR threshold but below the OVP threshold and off otherwise. This pin is capable to sink 10mA (minimum) current to drive an LED. The maximum voltage rating for this pin is 7V. This pin is independent on the EN-pin input.

**CHG** - Open-drain charge indication pin. This pin outputs a logic LOW when a charge cycle starts and turns to HIGH when the end-of-charge (EOC) condition is qualified. This pin is capable to sink 10mA min. current to drive an LED. When the charger is disabled, the CHG outputs high impedance.

**EN** - Enable input. This is a logic input pin to disable or enable the charger. Drive to HIGH to disable the charger. When this pin is driven to LOW or left floating, the charger is enabled. This pin has an internal  $200 \text{k}\Omega$  pull-down resistor.

GND - System ground.

**IMIN** - End-of-charge (EOC) current program pin. Connect a resistor between this pin and the GND pin to set the EOC

current. The EOC current IMIN can be programmed by the following equation:

$$I_{MIN} = \frac{11000}{R_{IMIN}}$$

(mA)

Where  $R_{IMIN}$  is in  $k\Omega$ . The programmable range covers 5% (or 10mA, whichever is higher) to 50% of IREF. When programmed to less than 5% or 10mA, the stability is not guaranteed.

**IREF** - Charge-current program and monitoring pin. Connect a resistor between this pin and the GND pin to set the charge current limit determined by the following equation:

$$I_{REF} = \frac{12089}{R_{IREF}}$$

(mA)

Where  $R_{IREF}$  is in  $k\Omega$ . The IREF pin voltage also monitors the actual charge current during the entire charge cycle, including the trickle, constant-current, and constant-voltage phases. When disabled, VIREF = 0V.

**BAT** - Charger output pin. Connect this pin to the battery. A  $1\mu F$  or larger X5R ceramic capacitor is recommended for decoupling and stability purposes. When the EN pin is pulled to logic HIGH, the BAT output is disabled.

**EPAD** - Exposed pad. Connect as much as possible copper to this pad either on the component layer or other layers through thermal vias to enhance the thermal performance.

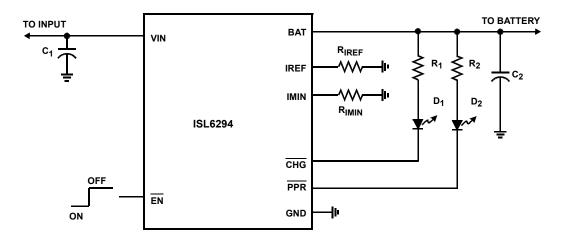

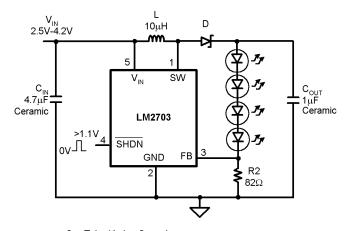

## **Typical Applications**

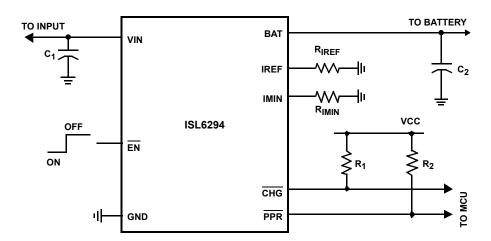

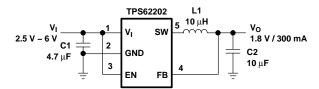

FIGURE 1. TYPICAL APPLICATION CIRCUIT INTERFACING TO INDICATION LEDS

#### **COMPONENT DESCRIPTION FOR FIGURE 1**

| PART                            | DESCRIPTION                          |  |  |  |

|---------------------------------|--------------------------------------|--|--|--|

| C <sub>1</sub>                  | 1μF X5R ceramic cap                  |  |  |  |

| C <sub>2</sub>                  | 1μF X5R ceramic cap                  |  |  |  |

| R <sub>IREF</sub>               | 24.3kΩ, 1%, for 500mA charge current |  |  |  |

| R <sub>IMIN</sub>               | 243kΩ, 1%, for 45mA EOC current      |  |  |  |

| R <sub>1</sub> , R <sub>2</sub> | 300Ω, 5%                             |  |  |  |

| D <sub>1</sub> , D <sub>2</sub> | LEDs for indication                  |  |  |  |

#### **COMPONENT DESCRIPTION FOR FIGURE 2**

| PART                                              | DESCRIPTION                            |  |  |

|---------------------------------------------------|----------------------------------------|--|--|

| C <sub>1</sub>                                    | 1μF X5R ceramic cap                    |  |  |

| C <sub>2</sub>                                    | 1μF X5R ceramic cap                    |  |  |

| R <sub>IREF</sub>                                 | F 24.3kΩ, 1%, for 500mA charge current |  |  |

| R <sub>IMIN</sub> 243kΩ, 1%, for 45mA EOC current |                                        |  |  |

| R <sub>1</sub> , R <sub>2</sub>                   | 100kΩ, 5%                              |  |  |

FIGURE 2. TYPICAL APPLICATION CIRCUIT WITH THE INDICATION SIGNALS INTERFACING TO A MCU

<u>intersil</u>

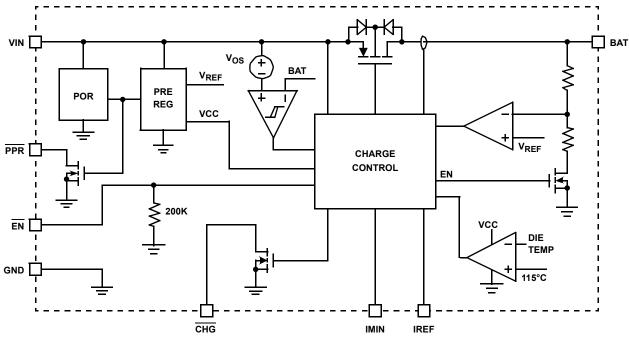

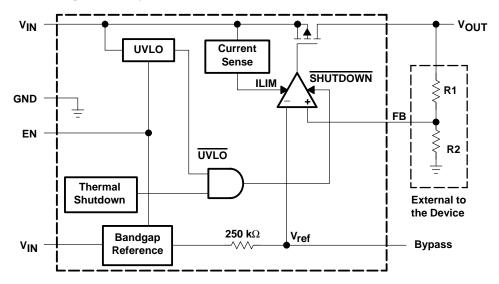

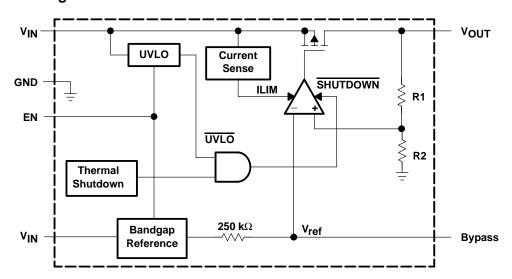

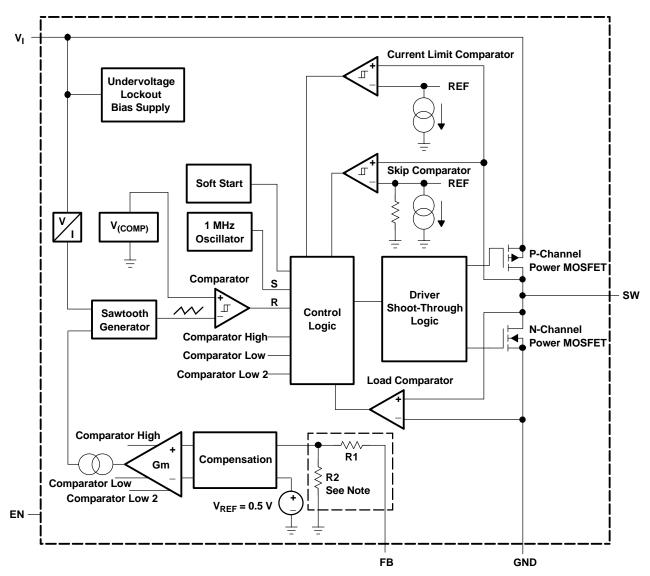

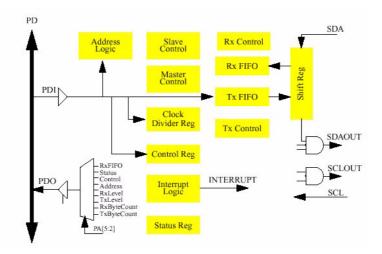

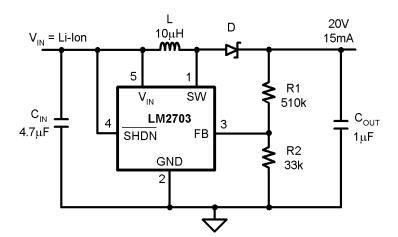

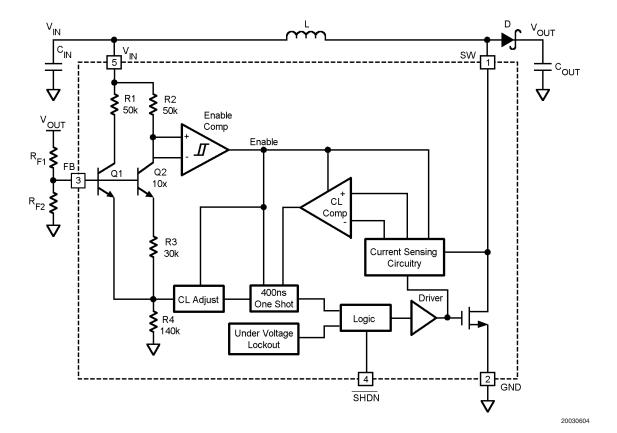

FIGURE 3. BLOCK DIAGRAM

## Description

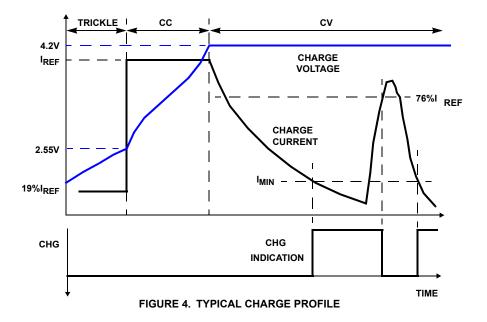

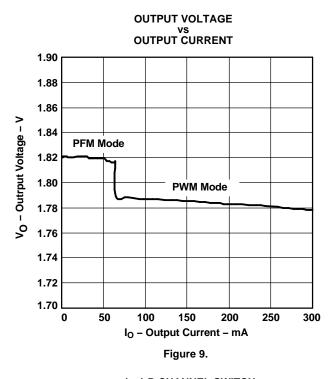

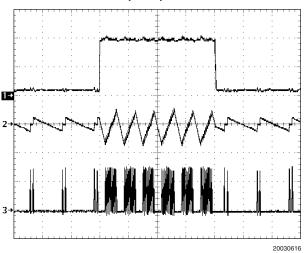

The ISL6294 charges a Li-ion battery using a CC/CV profile. The constant current  $I_{REF}$  is set with the external resistor  $R_{IREF}$  (See Figure 1) and the constant voltage is fixed at 4.2V. If the battery voltage is below a typical 2.55V trickle-charge threshold, the ISL6294 charges the battery with a trickle current of 19% of  $I_{REF}$  until the battery voltage rises above the trickle charge threshold. Fast charge CC mode is maintained at the rate determined by programming  $I_{REF}$  until the cell voltage rises to 4.2V. When the battery voltage

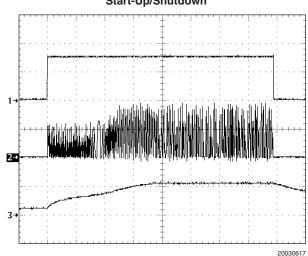

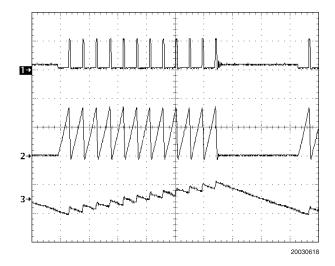

reaches 4.2V, the charger enters a CV mode and regulates the battery voltage at 4.2V to fully charge the battery without the risk of over charge. Upon reaching an end-of-charge (EOC) current, the charger indicates the charge completion with the CHG pin, but the charger continues to output the 4.2V voltage. Figure 4 shows the typical charge waveforms after the power is on.

The EOC current level IMIN is programmable with the external resistor R<sub>IMIN</sub> (See Figure 1). The CHG signal turns

to LOW when the trickle charge starts and rises to HIGH at the EOC. After the EOC is reached, the charge current has to rise to typically 76% I<sub>REF</sub> for the CHG signal to turn on again, as shown in Figure 4. The current surge after EOC can be caused by a load connected to the battery.

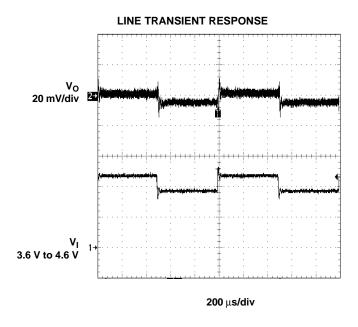

A thermal foldback function reduces the charge current anytime when the die temperature reaches typically 115°C. This function guarantees safe operation when the printed-circuit board (PCB) is not capable of dissipating the heat generated by the linear charger. The ISL6294 accepts an input voltage up to 28V but disables charging when the input voltage exceeds the OVP threshold, typically 6.8V, to protect against unqualified or faulty ac adapters.

#### **PPR Indication**

The PPR pin is an open-drain output to indicate the presence of the ac adapter. Whenever the input voltage is higher than the POR threshold, the PPR pin turns on the internal open-drain MOSFET to indicate a logic LOW signal, independent on the EN-pin input. When the internal open-drain FET is turned off, the PPR pin should leak less than 1µA current. When turned on, the PPR pin should be able to sink at least 10mA current under all operating conditions.

The PPR pin can be used to drive an LED (see Figure 1) or to interface with a microprocessor.

## Power-Good Range

The power-good range is defined by the following three conditions:

- 1. VIN > VPOR

- 2. VIN VBAT > VOS

- 3. VIN < VOVP

where the VOS is the offset voltage for the input and output voltage comparator, discussed shortly, and the VOVP is the overvoltage protection threshold given in the Electrical Specification. All  $\mathsf{V}_{POR},\,\mathsf{V}_{OS},\,\mathsf{and}\,\,\mathsf{V}_{OVP}$  have hysteresis, as given in the Electrical Specification table. The charger will not charge the battery if the input voltage is not in the powergood range.

## Input and Output Comparator

The charger will not be enabled unless the input voltage is higher than the battery voltage by an offset voltage VOS. The purpose of this comparator is to ensure that the charger is turned off when the input power is removed from the charger. Without this comparator, it is possible that the charger will fail to power down when the input is removed and the current can leak through the PFET pass element to continue biasing the POR and the Pre-Regulator blocks shown in the Block Diagram.

#### CHG Indication

The CHG is an open-drain output capable to at least 10mA current when the charger starts to charge and turns off when the EOC current is reached. The CHG signal is interfaced either with a micro-processor GPIO or an LED for indication.

#### EN Input